#### **CHAPTER 1: INTRODUCTION**

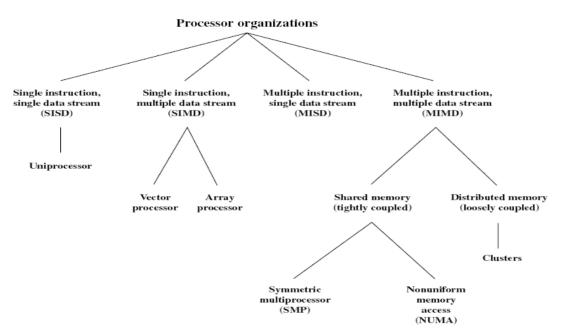

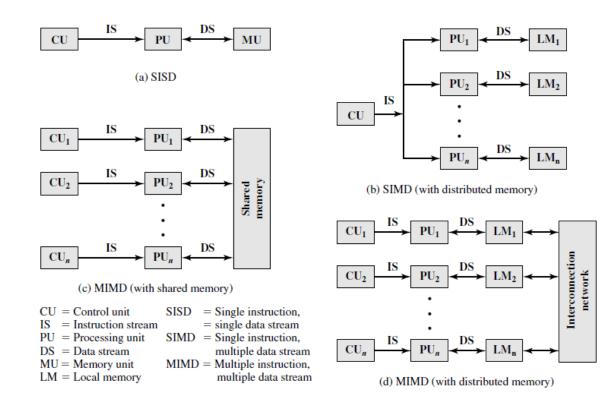

Why do we need to study computer organization and/or architecture ?

The computer lies to the heart of computing without it most of the computing disciplines today would be branch of theoritical mathematics. To be a professional in any field of computing today, one should not regard the computer as just a black box that executes programs by magic. All students of computing should acquire some understanding and appereciation of a computer system's fuctional componensts, their charactersitcis ,their performance and their interaction. Students needs to understand computer archtecture in order to structure a program so that it runs more efficiently on real machines.

Example: we need 6 bit system and there is available and there is available of 2bits,4 bits or 8 bits, now one should know which will be more beneficial using 2,2,2 bits bits or 4,4 bits system or 8 bit system and design the system according.

Choosing the best alternative for right organization.

Concept used in computer organization & computer architecture can be used o other courses fields.

#### *Computer architecture:*

- Computer architecture refers to those attributes of a system visible to a programmer or that have direct impact on the logical execution of a program.

- Computer architecture is the study of the structure, behavior and design of a computer system.

Examples of architectural attributes include:

- Instruction set.

- Number of bits used to represent various data types.

- I/O mechanism and techniques for addressing memory.

#### *Computer Organization:*

Computer organization refers to the operational units and their interconnection that realize the architectural specification.

- Organization attributes include those hardware details transparent to the programmer, such as control signals, interfaces, technologies used.

For example, it is an architectural design issue whether a computer will have multiple instruction or not, it is an organizational issue whether that instruction will be implemented by a special multiply unit or by a mechanism of repeated addition. The organization decision may be based on the anticipated frequency of use of multiply instruction, the relative speed of the approaches and the cost of the physical size of special multiply unit. The computer architecture of a computer system may be same with different organization.

# History of computer/ Miles stones in computer organization

### Mechanical era (1623-1945):

- The idea of using machines to solve mathematical problems can be traced back to 17th century where mathematician designed and implemented calculators that were capable of addition, subtraction, multiplication & division included Wilhelm Schickhard, Blaise Pascal, Gottfried Leibnitz.

- The first multi-purpose programmable computing device was Charles Babbage's difference and analytical engine.

- First commercial use of mechanical computers was in US census Bureau by Herman Hollerith.

Two major drawbacks of mechanical computers are :

- 1. Speed of operation limited by the inertia of moving parts.

- 2. Cumbersome unreliable and expensive.

# Electronic era

# First Generation (1945-1956)

- Vacuum tubes for circuitry, magnetic drum for memory.

- Enormous high power.

- ENIAC(Enhanced Numeric Integrator and Computer)

## Second generation (1956-1963)

- Transistors.

- Smaller, faster, cheap, more energy efficient more reliable.

- More complex arithmetic and logic unit, control units.

## Third generation (1964-1971)

- Integrated circuits, SSI (Small Scale Integration)-1 million transistors.

- LSI (Large Scale Integration)-10 million transistors.

- Third generation computer through keyboards and monitors and interface with an operating system, which allowed the device to run many different applications at one time with central program that monitored the memory.

#### Fourth Generation (1971-present)

- Used micro-processor, fourth generation of computers as thousands of integrated circuits were built on a single silicon chip.

- Intel 4004 chip developed in 1971 located all the components of the computer from CPU to memory to I/O controls on a single chip.

- IBM introduced first computer, 1984 apple macintosh

#### Fifth Generation (Present)

- Based on artificial intelligence, still development phases.

- Voice recognition, self-decision, nano technology, self-organization.

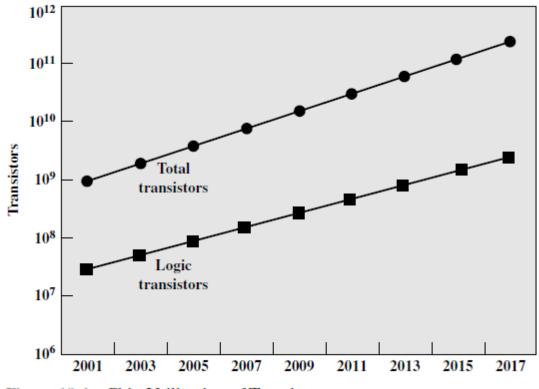

Moore's law: Moore observed that the number of transistors that would be put on a single chip was doubling every year and was corrected many years. This pace slowed to a doubling every 18 months in 1970.

#### Von neuman machine/IAS computer:

It was designed by the Princeton institute for advanced studies (IAS)

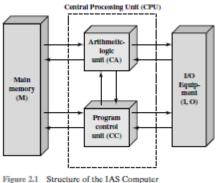

It consists of:

- Main memory: which stores both data and instruction.

- Arithmetic and logic unit: capable of operating on binary data.

- A control unit which interprets the instruction in memory and causes them to be executed.

#### Memory location

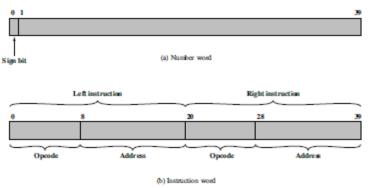

- 1000 storage locations called words of 40 binary digits (bits).

- Both data and instruction stored.

- All numbers and data represents in binary form.

- Each number represented by 1 sign bit, 39 bits value or two 20 bits instruction consisting of 8 bits opcode, 12 bits addressing address.

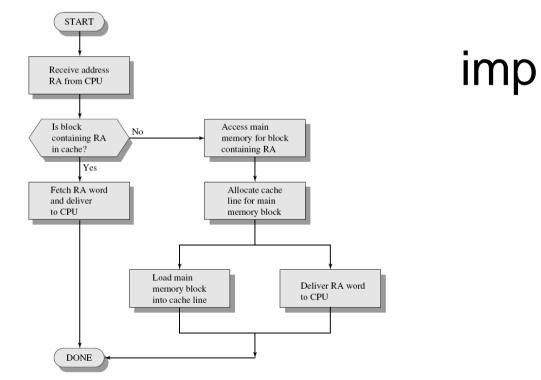

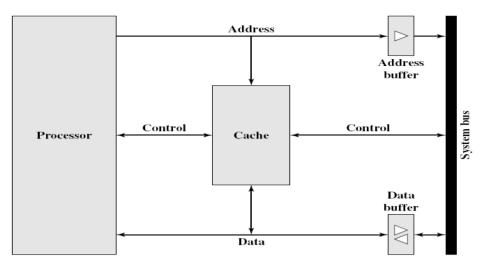

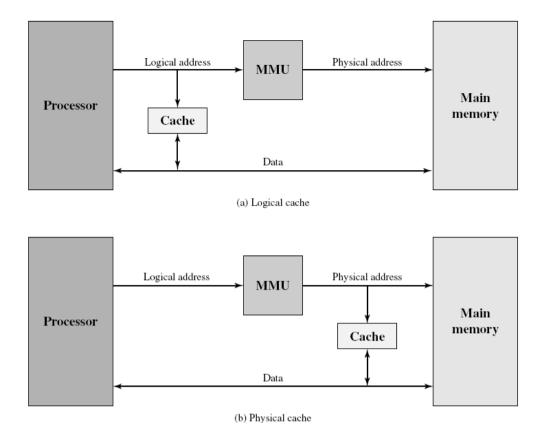

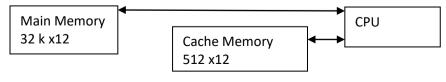

imp

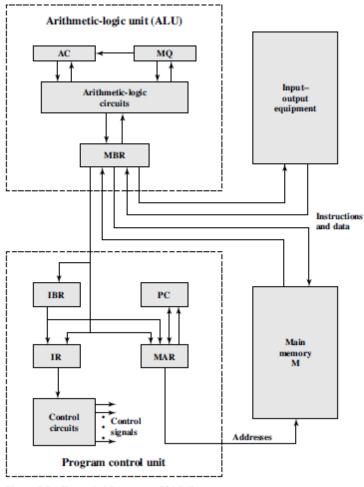

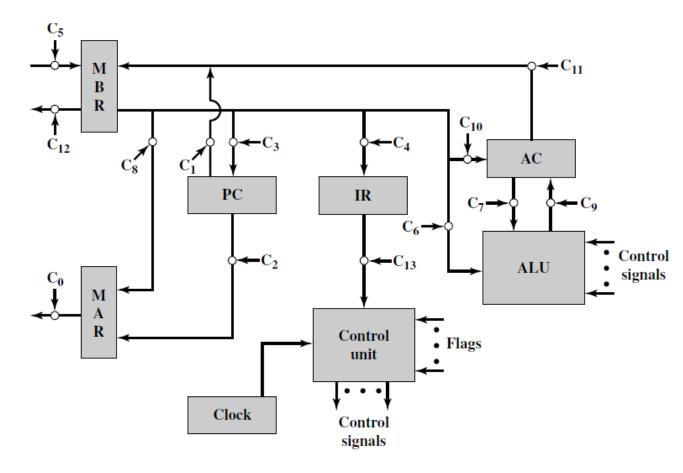

Figure 2.3 Expanded Structure of IAS Computer

#### **Different registers**

**Memory buffer register (MBR):** Contains a word to be stored in memory or sent to the I/O unit, or is used to receive a word from memory or from the I/O unit.

**Memory address register (MAR):** Specifies the address in memory of the word to be written from or read into the MBR.

Instruction register (IR): Contains the 8-bit opcode instruction being executed.

**Instruction buffer register (IBR):** Employed to hold temporarily the right hand instruction from a word in memory.

**Program counter (PC):** Contains the address of the next instruction-pair to be fetched from memory.

Accumulator (AC) and multiplier quotient (MQ): Employed to hold temporarily operands and results of ALU operations.

# Operation

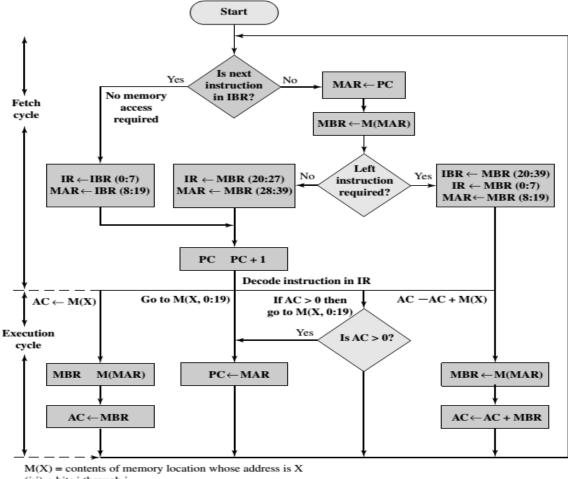

IAS operates by repetitively performing an instruction cycle. Instruction cycle contains fetch and execute cycle.

Fetch cycle

- The opcode of the next instruction is loaded into IR and addr. portion into MAR.

- The instruction can be taken from IBR from MBR and then to IBR, IR and MAR.

Execute cycle

- Control circuitry interprets the opcode and executes the instruction by sending out the appropriate control signal to cause data to be moved or perform ALU operations.

The total of 21 instructions that can be grouped onto:

1. **Data transfer:** between memory and/ OR ALU registers.

2. **Unconditional branch:** Normally, the control unit executes instructions in sequence from memory. This sequence can be changed by a branch instruction, which facilitates repetitive operations.

3. **Conditional branch:** The branch can be made dependent on a condition, thus allowing decision points.

4. **Arithmetic:** Operations performed by the ALU.

5. **Address modify:** Permits addresses to be computed in the ALU and then inserted into instructions stored in memory. This allows a program considerable addressing flexibility.

Table 2.1 The IAS Instruction Set

| Instruction<br>Type | Opcode   | Symbolic<br>Representation | Description                                                                                         |  |

|---------------------|----------|----------------------------|-----------------------------------------------------------------------------------------------------|--|

|                     | 00001010 | LOAD MQ                    | Transfer contents of register MQ to the accumulator AC                                              |  |

|                     | 00001001 | LOAD MQ,M(X)               | Transfer contents of memory location X to MQ                                                        |  |

|                     | 00100001 | STOR M(X)                  | Transfer contents of accumulator to memory location X                                               |  |

| Data transfer       | 00000001 | LOAD M(X)                  | Transfer M(X) to the accumulator                                                                    |  |

|                     | 00000010 | LOAD -M(X)                 | Transfer $-M(X)$ to the accumulator                                                                 |  |

|                     | 00000011 | LOAD  M(X)                 | Transfer absolute value of $M(X)$ to the accumulator                                                |  |

|                     | 00000100 | LOAD -  M(X)               | Transfer $- M(X) $ to the accumulator                                                               |  |

| Unconditional       | 00001101 | JUMP M(X,0:19)             | Take next instruction from left half of M(X)                                                        |  |

| branch              | 00001110 | JUMP M(X,20:39)            | Take next instruction from right half of M(X)                                                       |  |

| Conditional         | 00001111 | JUMP+ M(X,0:19)            | If number in the accumulator is nonnegative, take next in-<br>struction from left half of M(X)      |  |

| branch              | 00010000 | JUMP+ M(X,20:39)           | If number in the accumulator is nonnegative, take next instruction from right half of $M(X)$        |  |

|                     | 00000101 | ADD M(X)                   | Add M(X) to AC; put the result in AC                                                                |  |

|                     | 00000111 | ADD  M(X)                  | Add  M(X)  to AC; put the result in AC                                                              |  |

|                     | 00000110 | SUB M(X)                   | Subtract M(X) from AC; put the result in AC                                                         |  |

|                     | 00001000 | SUB  M(X)                  | Subtract $ M(X) $ from AC; put the remainder in AC                                                  |  |

| Arithmetic          | 00001011 | MUL M(X)                   | Multiply M(X) by MQ; put most significant bits of result<br>in AC, put least significant bits in MQ |  |

|                     | 00001100 | DIV M(X)                   | Divide AC by $M(X)$ ; put the quotient in MQ and the remainder in AC                                |  |

|                     | 00010100 | LSH                        | Multiply accumulator by 2; i.e., shift left one bit position                                        |  |

|                     | 00010101 | RSH                        | Divide accumulator by 2; i.e., shift right one position                                             |  |

| Address             | 00010010 | STOR M(X,8:19)             | Replace left address field at $M(X)$ by 12 rightmost bits of AC                                     |  |

| modify              | 00010011 | STOR M(X,28:39)            | Replace right address field at $M(X)$ by 12 rightmost bits of AC                                    |  |

# Table: IAS instruction set

\*\* see intel/Pentium generations table from william stalling book Computer Organization and

# **Architecture Designing for Performance**

# **Operations**

-IAS operates by repetitively performing an instruction cycle. -instruction cycle- fetch and execute cycle Fetch cycle

- op-code of the next instruction is loaded into IR & address portion into MAR.

- The instruction can be taken from IBR or from MBR and then to IBR, IR and MAR

## Execute cycle

- Control circuitry interprets the op-code and executes the instruction by sending out the appropriate control signals to cause data to be moved or perform ALU operations.

The total of 21 instruction can be grouped into:

- 1. data transfer: between memory and OR ALU register.

- 2. Conditional branch

- 3. Un-conditional branch

- 4. Arithmetic

- 5. Address modify: permits address to be computed in the ALU and then inserted into instruction in memory

Partial flowchart of IAS operation from William Stalling book.

(i:j) = bits i through j

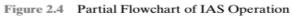

### Functional view of computer

#### Functions

- Data processing

- Data storage

- Data movement

- Control

#### **Instruction Fetch and Execute**

Figure 1.1 A Functional View of the Computer

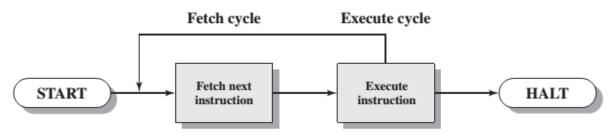

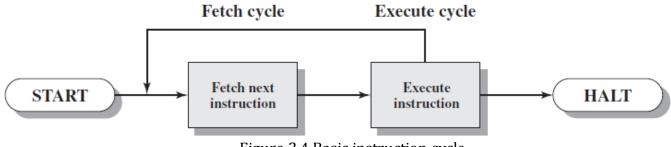

Figure 3.3 Basic Instruction Cycle

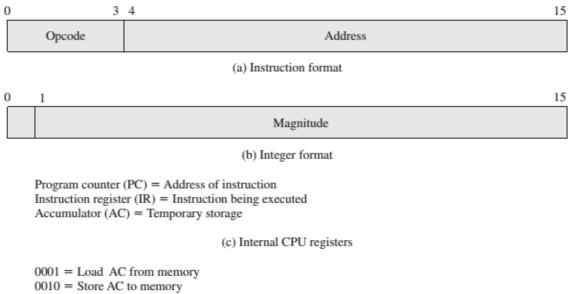

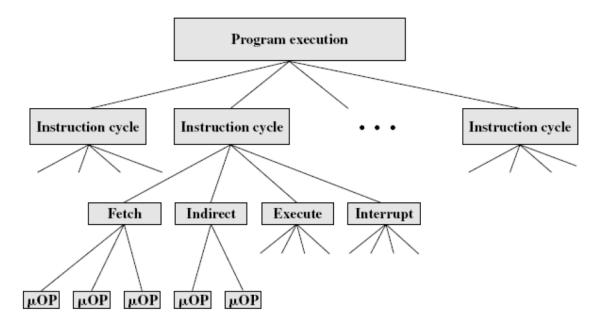

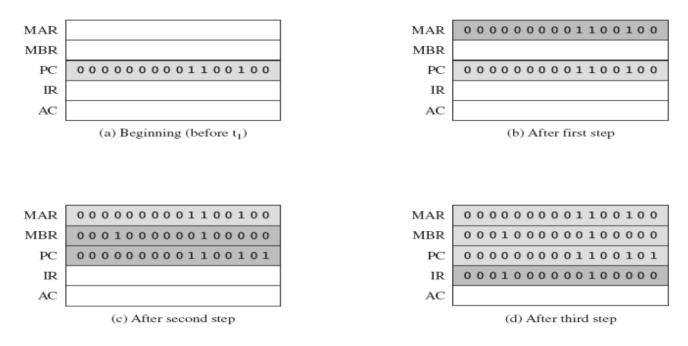

At the beginning of each instruction cycle, the processor fetches an instruction from memory. In a typical processor, a register called the program counter (PC) holds the address of the instruction to be fetched next. Unless told otherwise, the processor always increments the PC after each instruction fetch so that it will fetch the next instruction in sequence. So, for example, consider a computer in which each instruction occupies one 16-bit word of memory. Assume that the program counter is set to location 300. The processor will next fetch the instruction at location 300. On succeeding instruction cycles, it will fetch instructions from locations 301, 302, 303, and so on. This sequence can also be altered as required. The fetched instruction is loaded into a register in the processor known as the instruction register (IR). The processor interprets the instruction and performs the required action. In general, these actions fall into four categories:

Processor-I/O: Data may be transferred to or from a peripheral device by transferring between the processor and an I/O module.

Data processing: The processor may perform some arithmetic or logical operations on data.

Control: An instruction may specify that the sequence of execution be altered.

# Example of fetch and execute cycle

0101 = Add to AC from memory

(d) Partial list of opcodes

Figure 3.5 Example of Program Execution (contents of memory and registers in hexadecimal)

Figure 3.5: Example of Program Execution (contents of memory and registers in hexadecimal) Figure 3.5 illustrates a partial program execution, showing the relevant portions of memory and processor registers. The program fragment shown adds the contents of the

memory word at address 940 to the contents of the memory word at address 941 and stores the result in the latter location. Three instructions, which can be described as three fetch and three execute cycles, are required:

- 1. The PC contains 300, the address of the first instruction. This instruction (the value 1940 in hexadecimal) is loaded into the instruction register IR and the PC is incremented. Note that this process involves the use of a memory address register (MAR) and a memory buffer register (MBR). For simplicity, these intermediate registers are ignored.

- 2. The first 4 bits (first hexadecimal digit) in the IR indicate that the AC is to be loaded. The remaining 12 bits (three hexadecimal digits) specify the address (940) from which data are to be loaded.

- 3. The next instruction (5941) is fetched from location 301 and the PC is incremented.

- 4. The old contents of the AC and the contents of location 941 are added and the result is stored in the AC.

- 5. The next instruction (2941) is fetched from location 302 and the PC is incremented.

- 6. The contents of the AC are stored in location 941.

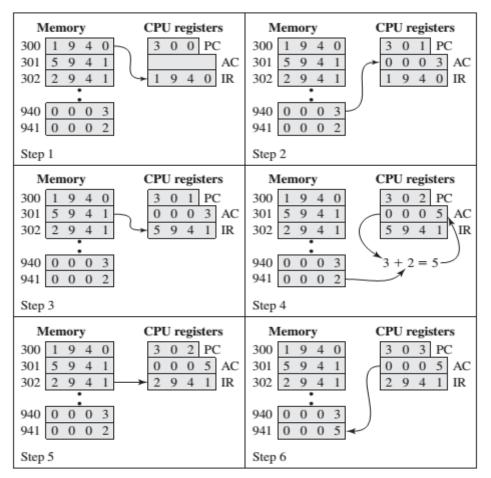

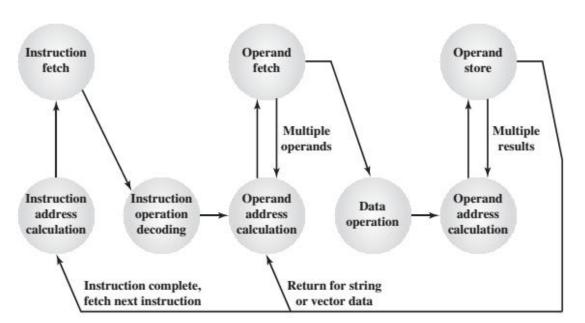

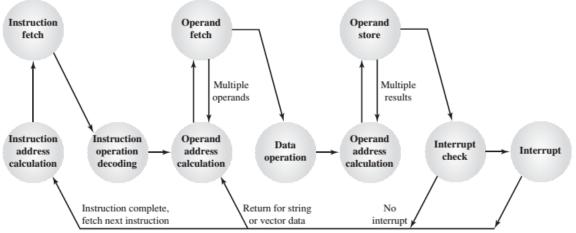

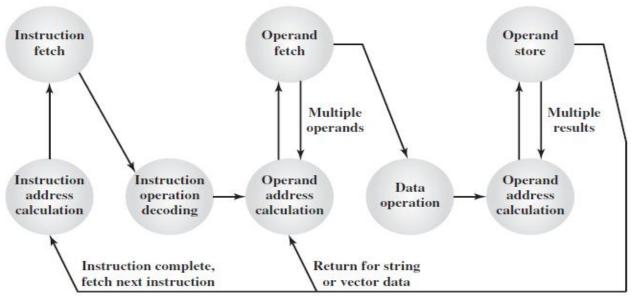

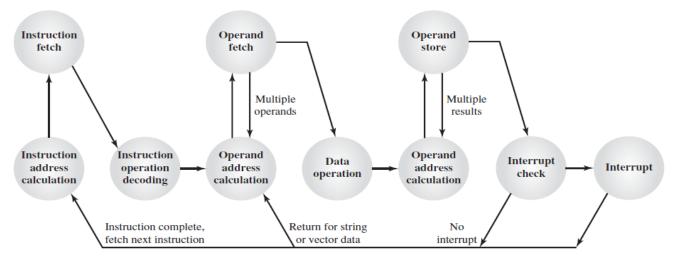

Figure 3.6 Instruction Cycle State Diagram

The above figure shows the sate diagram of instruction cycle, for any given instruction cycle. Some states may be null and other may be visited more than once. The different states can be described as:

- **Instruction address calculation (iac):** Determine the address of the next instruction to be executed. Usually, this involves adding a fixed number to the address of the previous instruction. For example, if each instruction is 16 bits long and memory is organized into 16-bit words, then add 1 to the previous address. If, instead, memory is organized as individually addressable 8-bit bytes, then add 2 to the previous address.

- **Instruction fetch (if):** Read instruction from its memory location into the processor.

- *Instruction operation decoding (iod):* Analyze instruction to determine type of operation to be performed and operand(s) to be used.

- **Operand address calculation (oac):** If the operation involves reference to an operand in memory or available via I/O, then determine the address of the operand.

- **Operand fetch (of):** Fetch the operand from memory or read it in from I/O.

- **Data operation (do):** Perform the operation indicated in the instruction.

- **Operand store (os):** Write the result into memory or out to I/O.

States in the upper part of Figure 3.6 involve an exchange between the processor and either memory or an I/O module. States in the lower part of the diagram involve only internal processor operations. The oac state appears twice, because an instruction may involve a read, a write, or both. However, the action performed during that state is fundamentally the

imp

same in both cases, and so only a single state identifier is needed. Also note that the diagram allows for multiple operands and multiple results, because some instructions on some machines require this.

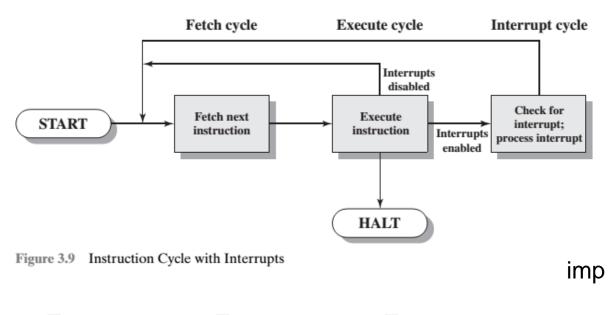

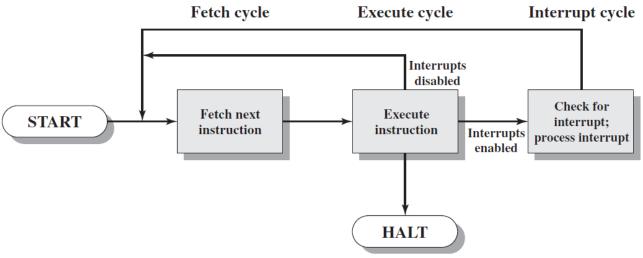

### Interrupts in instruction cycle

Interrupts is an asynchronous service request from hardware or software to CPU. Interrupts make the CPU execution of it's normal operation to pause to service external devices or errors. The processor and the OS are responsible for recognizing in interrupt suspending the user program, servicing the interrupt and then resuming the user program. The instruction cycle with interrupts is as shown below:

Figure 3.12 Instruction Cycle State Diagram, with Interrupts

#### **Instruction format**

An instruction format defines the layout of the bits of an instruction, in terms of its constituent fields. An instruction format must include an opcode and, implicitly or

explicitly, zero or more operands. Each explicit operand is referenced using one of the addressing modes. The format must, implicitly or explicitly, indicate the addressing mode for each operand. Some of the key design issue are:

# **Instruction Length**

The decision of instruction format length is affected by, memory size, memory organization, bus structure, processor complexity, and processor speed. The most obvious trade-off here is between the desire for a powerful instruction and a need to save space. Programmers want more opcodes, more operands, more addressing modes, and greater address range. More opcodes and more operands make life easier for the programmer, because shorter programs can be written to accomplish given tasks. Similarly, more addressing modes give the programmer greater flexibility in implementing certain functions, such as table manipulations and multiple-way branching. And, of course, with the increase in main memory size and the increasing use of virtual memory, programmers want to be able to address larger memory ranges. All of these things (opcodes, operands, addressing modes, address range) require bits and push in the direction of longer instruction lengths. But longer instruction length may be wasteful. Another trade off, consideration may be either instruction length should be equal to the memory transfer length or multiple, otherwise we will not get an integral number of instruction during fetch cycle.

# **Allocation of Bits**

For a given instruction length, there is clearly a trade-off between the number of op-codes and the power of the addressing capability. More op-codes obviously mean more bits in the op-code field. For an instruction format of a given length, this reduces the number of bits available for addressing. There is one interesting refinement to this trade-off, and that is the use of variable-length op-codes. In this approach, there is a minimum op-code length but, for some op-codes, additional operations may be specified by using additional bits in the instruction. For a fixed-length instruction, this leaves fewer bits for addressing. Thus, this feature is used for those instructions that require fewer operands and/or less powerful addressing. The following interrelated factors go into determining the use of the addressing bits.

• **Number of addressing modes:** Sometimes an addressing mode can be indicated implicitly. For example, certain op-codes might always call for indexing. In other cases, the addressing modes must be explicit, and one or more mode bits will be needed.

**Number of operands:** Typical instructions on today's machines provide for two operands. Each operand address in the instruction might require its own mode indicator, or the use of a mode indicator could be limited to just one of the address fields.

• **Register versus memory:** With a single user-visible register (usually called the accumulator), one operand address is implicit and consumes no instruction bits. However, single-register programming is awkward and requires many instructions. Even with multiple registers, only a few bits are needed to specify the register. The more that registers can be used for operand references, the fewer bits are needed.

• **Number of register sets:** Machines have one set of general purpose registers, with typically 32 or more registers in the set. These registers can be used to store data and can be used to store addresses for displacement addressing. Some architectures have a collection of two or more specialized sets (such as data and displacement). One advantage

of this latter approach is that, for a fixed number of registers, a functional split requires fewer bits to be used in the instruction. For example, with two sets of eight registers, only 3 bits are required to identify a register; the op-code or mode register will determine which set of registers is being referenced.

• Address range: the range of addresses that can be referenced is related to the number of address bits. Because this imposes a severe limitation, direct addressing is rarely used. With displacement addressing, the range is opened up to the length of the address register. Even so, it is still convenient to allow rather large displacements from the register address, which requires a relatively large number of address bits in the instruction.

• Address granularity: In a system with 16 or 32 bits word or address can reference a word or a byte at designers choice. Byte addressing is convenient for character manipulation but required for a fixed sixe of memory more address bits.

**Variable length instruction:** The instruction discussed so far have single fixed length, but the designer may choose instead to provide a variety of instruction formats of different lengths, this tactic makes it easy to provide a large no. of op-codes with different lengths and the address length can also be varied with variable length instruction, these many variations can be provided efficiently and compactly.

# Instruction representation

Within the computer each instruction is represented by a sequence of bits. The instruction is divided into fields, corresponding to the constituents elements of the instruction. It is difficult for both the programmer and reader to deal with binary representation, so it is

common to use symbolic representation. Code are represented by abbreviations called nmemonics that indicate the operations.

ADD: Add, SUB: Subtract, MUL: Multiply, DIV: Divide.

Instruction types

An instruction set should be functionally complete. It should formulate any high level data processing task. Such operations can be grouped as:

- 1. Data processing: ALU

- 2. Data movement: I/O instruction

- 3. Data storage: memory instruction

- 4. Control operations: test and branch instruction.

Good instruction set should meet following standards:

- 1. Completeness: to be able to construct a machine level program to evaluate any computable function.

- 2. Efficient: frequently performed instruction should be done quickly with few instructions.

- 3. Regular and complete class of instruction: provide logical set of operations.

- 4. Orthogonal: define instruction, data types and addressing independently.

- 5. Compatible: with existing hardware and software product of that time.

# Number of address/ address in an instruction

In a typical arithmetic or logical instruction 3 address is required, 2 for operands and 1 for result. These address can be explicitly given or implied by instruction. Example: compare instruction Y = (A-B)/[C+(D\*E)] with one, two and three instructions

# 3-address instruction

Both operands and the destination for the result are explicitly contained in the instruction word.

| Instruction | Comment |

|-------------|---------|

| SUB Y,A,B   | Y←A-B   |

| MUL T,D,E   | T←D*E   |

| ADD T,T,C   | T←T+C   |

| DIV Y,Y,T   | Y←Y/T   |

This format is rarely used due to the length of address themselves and resulting length of the instruction word.

## 2-address instruction

One of the address is used to specify both an operand and result location. Very common in instruction set.

| Instruction | Comment |

|-------------|---------|

| MOV Y,A     | Y←A     |

| SUB Y,B     | Ү←Ү-В   |

| MOV T,D     | T←D     |

| MUL T,E     | T←T*E   |

| ADD T,C     | T←T+C   |

| DIV Y,T     | Y←Y/T   |

# 1-address instruction

Traditional accumulator based operations, ACC ← ACC+X

| Instruction | Comment |

|-------------|---------|

| LOAD D      | AC←D    |

| MUL E       | AC←AC*E |

| ADD C       | AC←AC+C |

| STOR Y      | Y←AC    |

| LOAD A      | AC←A    |

| SUB B       | AC←AC-B |

| DIV Y       | A←AC/Y  |

| STOR Y      | Y←AC    |

### 0 address instruction

Zero address instruction are applicable to a special memory organization called stack. A stack is a last-in-first-out set of locations. Zero address instruction would reference the top of the two stack elements.

| PUSH A | TOS←A                           |

|--------|---------------------------------|

| PUSH B | TOS←B                           |

| SUB    | TOS←(A-B)                       |

| PUSH D | TOS←D                           |

| PUSH E | TOS←E                           |

| MUL    | TOS←D*E                         |

| PUSH C | TOS←C                           |

| ADD    | TOS←C+(D*E)                     |

| DIV    | $TOS \leftarrow (A-B)/(C+D^*E)$ |

| POP Y  | Y←TOS                           |

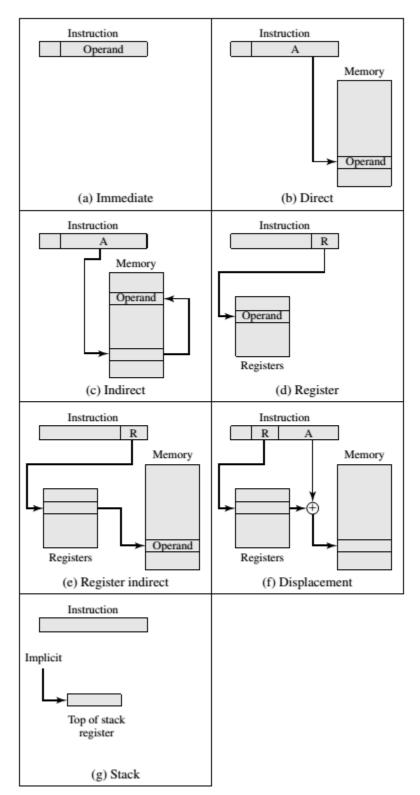

## Addressing mode

The manner in which each address field specifies memory location is called addressing modes. That can be of following

#### 1. Immediate mode:

The operand is contained within the instruction itself. Data is a constant at run time. No additional memory reference are required after the fetch of the instruction. Size of the operand is limited, i.e range of value limited.

**Operand A**

## 2. Direct addressing mode:

The address field of the instruction contains the effective address of the operand. No calculation required. One additional memory access is required to fetch the operand. Address range is limited by the width of the field that contains the address reference. Address is a constant at run time but data itself can be changed during the program execution.

EA=A

### 3. Indirect addressing:

The address filed in the instruction specified a memory location which contains the address of the data. In indirect addressing, address field refer to the address of a word in memory which in-turn contains a full length address of operand.

#### 4. Register based addressing modes

Register addressing: similar to direct addressing the only difference is that the address field refers to a register rather than a main memory address.

EA=R

*Register indirect:* like indirect, but address filed specifies a register that contains the effective address.

#### Advantage

i. Only a small address filed is needed in the instruction.

ii. No time consuming memory reference are required.

Dis-advantage

- i. If registers are heavily used, this will limit the performance of the processor.

- ii. If frequently used there will be more immediate steps involved. So only used if the operand in a register remains in use for multiple operations.

#### 5. Displacement or address relative addressing

## EA=A+(R)

Displacement address requires that the instruction have two address filed at least one of which is explicit (definite). The value contained in one address field (value=A) is directly added to a register to produce effective address. The most commonly used displacement addressing:

#### a. Relative addressing:

- A is added to the program counter contents to cause a branch operations in fetching the next instruction.

## **b.** Base register addressing:

- The referenced register contains a main memory address and the address register field contains a displacement (usually unsigned integer) from that address.

## c. Indexing:

The address field references a main memory address and the referenced register contains a positive displacement from that address.

## 6. Stack addressing:

A stack is a linear array of location. It is sometime referred to as a pushdown list or last-infirst-out queue. Items are appended to the top of the stack so that at any given time the block is partially filled. Associated with stack is a pointer whose value is the address of the top of the stack. Alternatively, the top two elements of the stack may be in processor register, in which case the stack pointer references the third element of the stack.

Figure 11.1 Addressing Modes

# Stack, reverse polish notation

A+B: infix notation +AB: prefix or polish notation AB+: postfix or reverse polish notation (A\*B+C\*D) in reverse polish notation is AB\*CD\*+

Scan the expression from let to right, when an operator is reached perform the operation with operands found on the left side of the operator. Remove the two operands and the operator and replace them by the number obtained from the result of the operation. Continue to scan the expression and repeat the procedure for every operator encountered until there are no more operators.

Example:  $(A+B)^*[C^*(D+E) +F]$

Convert to reverse polish notation

- First perform all arithmetic inside the inner parameters.

- Then inside outer parentheses.

- Do multiplication and division before addition and subtraction operations.

Final result is: AB+DE+C\*F+\*

**\*\*Note:** examples of computer families, see table 2.3 for IBM 700/7000 series, IBM system/360

The evolution of intel x86 architecture, see table 2.6 from William stallings

Future trends in computer

- ARM, embedded system

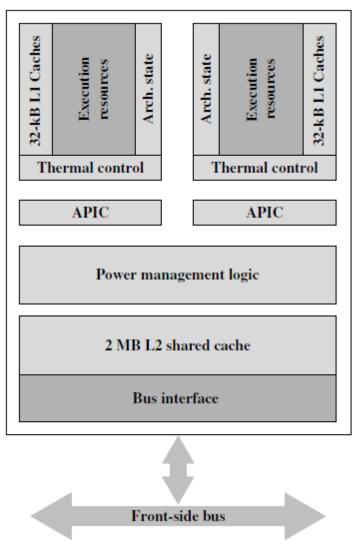

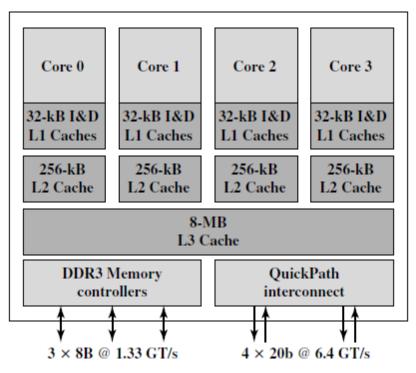

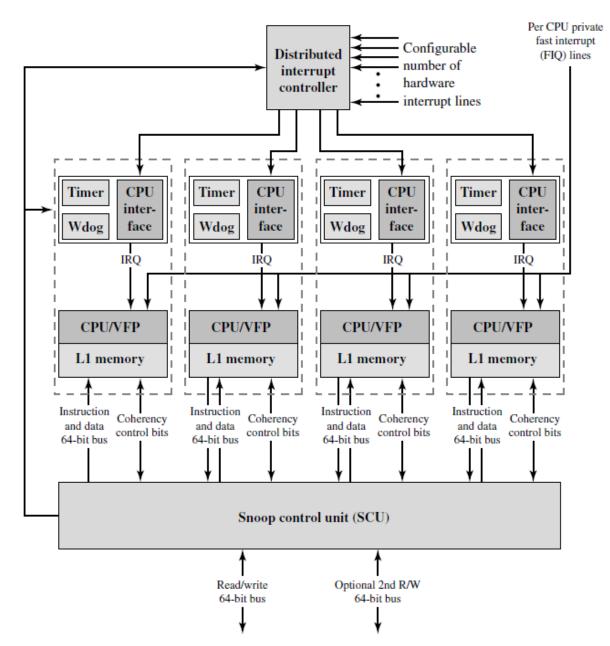

## **Designing computer for performance**

Year by year, the cost of computer systems continues to drop dramatically, while the performance and capacity of those systems continue to rise equally dramatically. Most of the today's computer requires some of the following capabilities:

- Image processing

- Speech recognition

- Videoconferencing

- Multimedia authoring

- Voice and video annotation of files

- Simulation modeling

Basically the building blocks for today's computer are virtually same as those of the IAS computer, but the techniques for making performance high has improved a lot and sophisticated. Now we highlight some of the driving factors behind the need to design for performance.

# • Microprocessor Speed

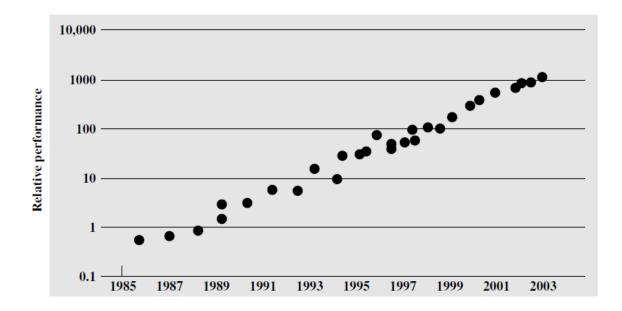

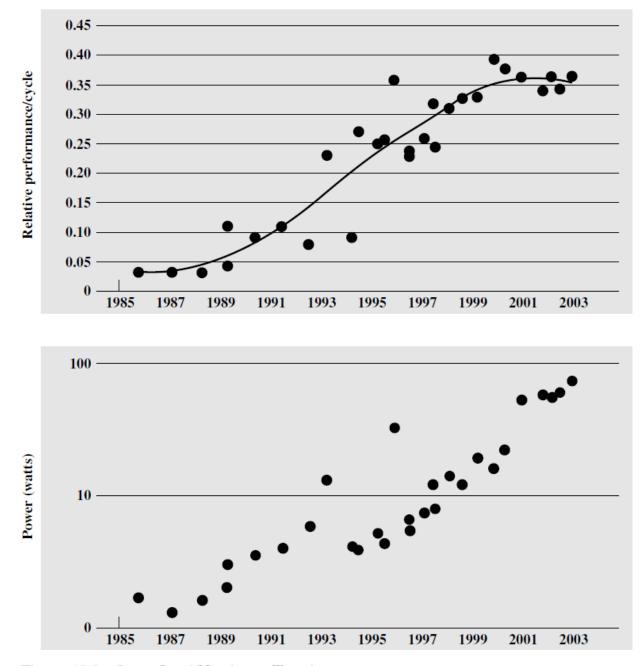

What gives these processors such mind-boggling power is the relentless pursuit of speed by processor chip manufacturers. The evolution of these machines continues to bear out Moore's law, mentioned previously. So long as this law holds, chipmakers can unleash a new generation of chips every three

Years with four times as many transistors. In memory chips, this has quadrupled the capacity of dynamic random-access memory (DRAM), still the basic technology for computer main memory, every three years. In microprocessors, the addition of new circuits, and the speed boost that comes from reducing the distances between them, has improved performance four or fivefold every three years. But the raw speed of the microprocessor will not achieve its potential unless it is fed a constant stream of work to do in the form of computer instructions. Anything that gets in the way of that smooth flow undermines the power of the processor. Accordingly, while the chipmakers have been busy learning how to fabricate chips of greater and greater density, the processor designers must come up with ever more elaborate techniques for feeding the monster. Among the techniques built into contemporary processors are the following:

- Branch prediction: The processor looks ahead in the instruction code fetched from memory and predicts which branches, or groups of instructions, are likely to be processed next. If the processor guesses right most of the time, it can prefetch the correct instructions and buffer them so that the processor is kept busy. The more sophisticated examples of this strategy predict not just the next branch but multiple branches ahead. Thus, branch prediction increases the amount of work available for the processor to execute.

- Data flow analysis: The processor analyzes which instructions are dependent on each other's results, or data, to create an optimized schedule of instructions. In fact, instructions are scheduled to be executed when ready, independent of the original program order. This prevents unnecessary delay.

- Speculative execution: Using branch prediction and data flow analysis, some processors speculatively execute instructions ahead of their actual appearance in the program execution, holding the results in temporary locations. This enables the processor to keep its execution engines as busy as possible by executing instructions that are likely to be needed.

## Performance Balance

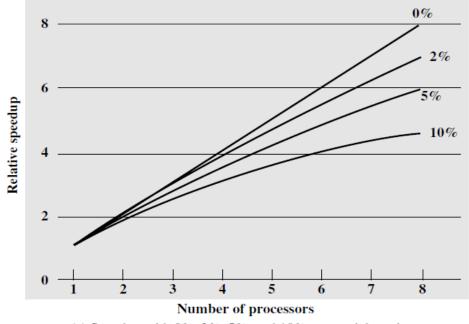

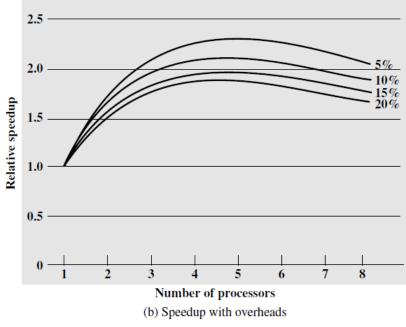

While processor power has raced ahead at breakneck speed, other critical components of the computer have not kept up. The result is a need to look for performance balance: an adjusting of the organization and architecture to compensate for the mismatch among the capabilities of the various components.

Consider an example the speed of processor has increased tremendously or rapidly but not the speed of data transfer from main memory to processor, so the processor has to wait for the data from memory to come causing processor stall or wait for data causing overall slow performance. The no of ways the system architect can solve this problem are:

- Increasing the number of bits that are retrieved from memory.

- Introducing a cache or other buffering schemes.

- Reducing the access to memory incorporating more caches.

- Using high speed buses for faster data transfer.

- Another example I/O peripheral devices. The key idea here is to balance the throughput and processing demands of the processor, main memory, I/O devices, inter connecting structures.

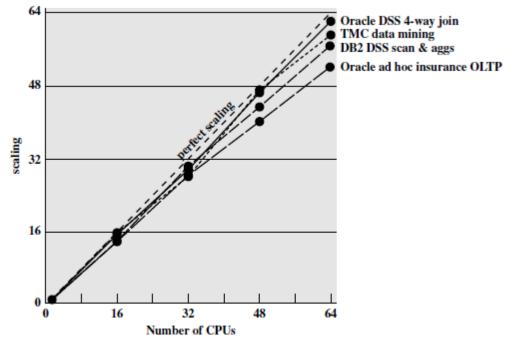

# Improvements in Chip Organization and Architecture

As designers wrestle with the challenge of balancing processor performance with that of main memory and other computer components, the need to increase processor speed remains. There are three approaches to achieving increased processor speed:

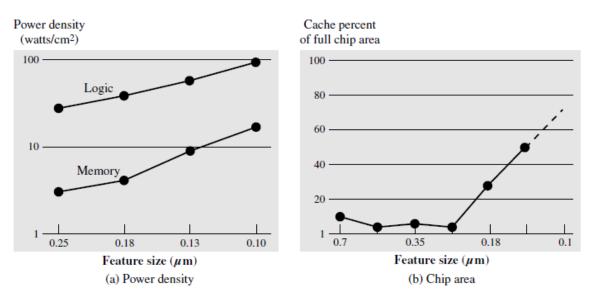

- **Increase the hardware speed of the processor:** This increase is fundamentally due to shrinking the size of the logic gates on the processor chip, so that more gates can be packed together more tightly and to increasing the clock rate. With gates closer together, the propagation time for signals is significantly reduced, enabling a speeding up of the processor. An increase in clock rate means that individual operations are executed more rapidly.

- Increase the size and speed of caches that are interposed between the processor and main memory. In particular, by dedicating a portion of the processor chip itself to the cache, cache access times drop significantly.

- Make changes to the processor organization and architecture that increase the effective speed of instruction execution. Typically, this involves using parallelism in one form or another.

Here are some obstacles or factors that limit or hold back in increasing the performance using above method.

- **Power:** As the density of logic and the clock speed on a chip increase, so does the power density (Watts/cm2). The difficulty of dissipating the heat generated on high-density, high-speed chips is becoming a serious design issue.

- **RC delay:** The speed at which electrons can flow on a chip between transistors is limited by the resistance and capacitance of the metal wires connecting them; specifically, delay increases as the RC product increases. As components on the chip decrease in size, the wire interconnects become thinner, increasing resistance. Also, the wires are closer together, increasing capacitance.

- **Memory latency:** Memory speeds lag processor speeds. Difference between access time of processor and memory.

Thus, there will be more emphasis on organization and architectural approaches to improving performance. Two main strategies that have been used to increase performance beyond what can be achieved simply by increasing clock speed are:

- Increasing cache capacity, using two or more levels of caches.

- Using parallel execution, like pipelining & superscalar methods.

Evolution of Intel X86 architecture see William stallings book on computer organization and architecture designing for performance.

# **Register Transfer and Micro operations**

Register Transfer and Register Transfer language(RTL)

# **Register Transfer Language**

A digital system is an interconnection of digital hardware modules that accomplishes a specific information-processing task. Digital modules are best defined by the registers they contain and the operations that are performed on the data stored in them. The operations executed on data stored is registers are called micro-operations. A micro-operation is an elementary operation performed on the information stored in one or more registers. The result of the operations may replace the previous binary information of a register or may be transferred to another register. Examples of micro-operations are shift, count, clear and load.

The internal hardware organization of a digital computer is best defined by specifying:

- 1) The set of registers it contains and their function.

- 2) The sequence of micro-operations performed on the binary information stored in the registers.

- 3) The control that initiates the sequence of micro-operations.

The process of specifying the micro-operations in the computer in descriptive explanations could be long and tedious. A more convenient way is to adopt a suitable symbolic notation to describe the micro-operations, transfer among registers is called register transfer language(RTL). A register transfer language is a system for expressing in symbolic form of micro-operations sequences among the register of a digital module.

Computer registers are those that hold the data, they are designated by capital letters to denote the function of the register, e.g. PC (Program Counter), IR (Instruction Register).

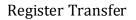

The individual flip-flops in an n-bit register are number in sequence from 0 through n-1, starting from 0 in the right most position and increasing the numbers towards left. Figure shows the representation of register block diagram. The name in the 16-bit register is PC, the

symbol PC (0-7) or PC(L) refers to the low-order byte and PC (8-15) or PC(H) to higher order byte.

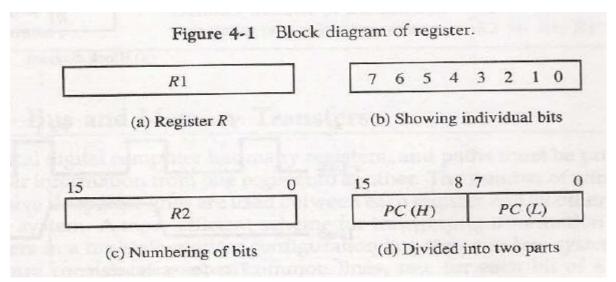

Information transfer from one register to another is designated in symbolic form by means of replacement operations. The statement  $R_2 \leftarrow R_1$  denotes a transfer of the content or register  $R_1$  into register  $R_2$ . It designates a replacement of the content of  $R_2$  by the content of  $R_1$ . By definition the content of the source register  $R_1$  does not change after transfer.

We want transfer to occur only under a predefined control condition. This can be shown by means of an if-then statement

If (P=1), then  $(R_2 \leftarrow R_1)$

Where P is a control signal generated in control section. It is sometimes convenient to separate the control variables from the register transfer operation by specifying a control function. A control function is a Boolean variables that is equal to 1 or 0. The control function is included in the statement as follows:  $P:R2 \leftarrow R1$

It symbolizes the requirement that the transfer operation be executed by hardware only if P=1.

Figure shows the block diagram that depicts the transfer from R1 to R2.

The n outputs of register  $R_1$ , are connected to the n inputs of register R<sub>2</sub>, register R<sub>2</sub> has a load input that is activated by control variable P. It is assumed that the control variable is synchronized with same clock as the one applied to the register. P is active in the control section by the rising edge of a clock pulse at time t. The next positive transition of the clock at time(t+1) find the load input active and data inputs of R<sub>2</sub> are then loaded into the register in parallel. P may go back 0 at time t+1, otherwise the transfer will occur with

every clock pulse transition while P remains active.

The statement  $T:R_2 \leftarrow R_1$ ,  $R_4 \leftarrow R_3$

Denotes an operation that exchanges the content of two register during one common clock pulse provided that T=1.

# Bus and memory transfer

In a digital computer there may be many register, so that there will be many data paths if separate lines are used between each register, so a more efficient way for transferring information between register in multiple register configuration in a common bus system. A bus structure consists of a set of common lines, one for each bit of register through which binary information is transferred one at a time.

The transfer of information from a bus into one of many destination register can be accomplished by connection the bus lines to the inputs of all destination registers and activation the load control of the particular destination register selected. When the bus is included in the statement the register transfer may be symbolized as

BUS  $\leftarrow$  C, R<sub>1</sub>  $\leftarrow$  BUS

The content of register C is placed on the bus and the content of the bus is loaded into register R1, by activating load control input. If bus is known to exist in the system, it may be convenient just to show the direct transfer

$R_1 \leftarrow C$

# **Memory transfer**

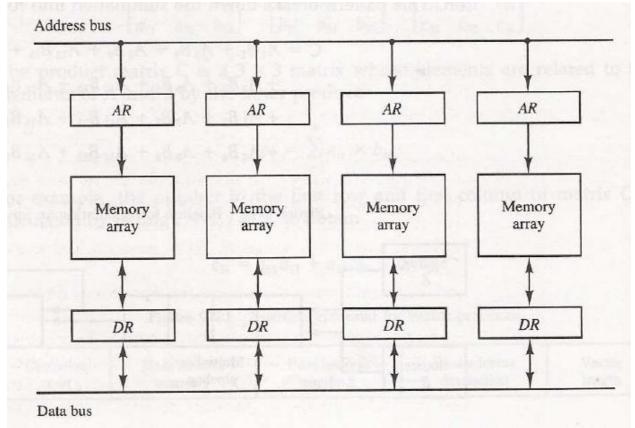

The transfer of information from memory word to the outside environment is called read operation. The transfer of new information to be stored into the memory is called write operation. A memory word will be symbolized by letter M. It is necessary to specify the address of M when writing memory transfer operations. This will be done by enclosing the address in square brackets following letter M.

## Example : read $DR \leftarrow M[R]$

Consider a memory unit that receives the address from a register called the address register(AR). The data are transferred to another register called data register(DR). This causes a transfer of information into DR from the memory word M selected by the address AR.

Example :  $R_3 \leftarrow R_1 + \overline{R_2} + 1$

Assume the input data are in register R<sub>1</sub>,  $\overline{R_2}$  is the symbol for the 1's complement of R<sub>2</sub>. Adding the content of R<sub>1</sub> to 2's complement of R<sub>2</sub> is equivalent to R<sub>1</sub>-R<sub>2</sub>.

Arithmetic micro-operations

| Symbolic designation                   | Description                                    |  |

|----------------------------------------|------------------------------------------------|--|

| $R3 \leftarrow R1 + R2$                | Contents of R1 plus R2 transferred to R3       |  |

| $R3 \leftarrow R1 - R2$                | Contents of R1 minus R2 transferred to R3      |  |

| $R2 \leftarrow \overline{R2}$          | Complement the contents of R2 (1's complement) |  |

| $R2 \leftarrow \overline{R2} + 1$      | 2's complement the contents of R2 (negate)     |  |

| $R3 \leftarrow R1 + \overline{R2} + 1$ | R1 plus the 2's complement of R2 (subtraction) |  |

| $R1 \leftarrow R1 + 1$                 | Increment the contents of R1 by one            |  |

| $R1 \leftarrow R1 - 1$                 | Decrement the contents of R1 by one            |  |

# Logical micro-operations

Logic micro-operations specify binary operations for strings of data bits stored in registers. These operations consider each bit of register separately and treat them as binary variables. For example, the exclusive-OR micro operations with the content of two register  $R_1$  and  $R_2$  is symbolized by the statement  $P:R_1 \leftarrow R_1 \oplus R_2$

It specifies a logic micro-operations to be executed on the individual bits of the register provided that the control variable P=1. Example consider  $R_1$  contains 1010 &  $R_2$  contains 1100. The exclusive –OR micro operation stated above symbolized the logical operations of logical XOR of individual bits.

| 1 | 0 | 1 | 0 |

|---|---|---|---|

| 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

The content of  $R_1$  after the execution of the micro-operations is equal the bit-by –bit exclusive OR on pairs of bits in  $R_2$  and previous value of  $R_1$ .

Special symbols

Special symbols will be adopted for the logic micro-operations of OR, AND and complement, to distinguish them from the corresponding symbols used to express Boolean functions. Example 'V' will be used to denote an OR , ' $\Lambda$ ' between R<sub>5</sub> & R<sub>6</sub> designated 'OR' micro-operations.

## Shift micro-operations

Shift micro-operations are used for serial transfer of data. They are used in conjunction with arithmetic, logical and other data processing operations. The content of a register can be shifted to the left or the right. The information transferred through the serial inputs determines the types of shift. There are three types of shift

1. Logical shift: a logical shift is one that transfers 0 through the serial input. We will adopt the symbol shl and shr for logical shift-left and shift right microoperations.

$R_1 \leftarrow shl R_1, R_2 \leftarrow shr R_2$

| Boolean function      | Microoperation                       | Name           |

|-----------------------|--------------------------------------|----------------|

| $F_0 = 0$             | $F \leftarrow 0$                     | Clear          |

| $F_1 = xy$            | $F \leftarrow A \land B$             | AND            |

| $F_2 = xy'$           | $F \leftarrow A \land \overline{B}$  |                |

| $F_3 = x$             | $F \leftarrow A$                     | Transfer A     |

| $F_4 = x'y$           | $F \leftarrow \overline{A} \land B$  |                |

| $F_5 = y$             | $F \leftarrow B$                     | Transfer B     |

| $F_6 = x \oplus y$    | $F \leftarrow A \oplus B$            | Exclusive-OR   |

| $F_7 = x + y$         | $F \leftarrow A \lor B$              | OR             |

| $F_8 = (x + y)'$      | $F \leftarrow \overline{A \lor B}$   | NOR            |

| $F_9 = (x \oplus y)'$ | $F \leftarrow \overline{A \oplus B}$ | Exclusive-NOR  |

| $F_{10} = y'$         | $F \leftarrow \overline{B}$          | Complement B   |

| $F_{11} = x + y'$     | $F \leftarrow A \lor \overline{B}$   |                |

| $F_{12} = x'$         | $F \leftarrow \overline{A}$          | Complement A   |

| $F_{13} = x' + y$     | $F \leftarrow \overline{A} \lor B$   |                |

| $F_{14} = (xy)'$      | $F \leftarrow \overline{A \land B}$  | NAND           |

| $F_{15} = 1$          | $F \leftarrow all 1's$               | Set to all 1's |

| 1 | 0 | 1 | 1 |

|---|---|---|---|

| 0 | 1 | 0 | 1 |

Above are two micro-operations that specify 1 bit to the left of the content of register  $R_1$  and 1bit shift to the right of the content of register  $R_2$ . The register symbol must be of the same on the both side of the arrow.

- 2. Circular shift: the circular shift (also known as rotate operations) circulates the bits of the register around the two ends without loss of information. This is accomplished by connecting the serial output of the shift register to its serial inputs. Use the symbol as cil or cir

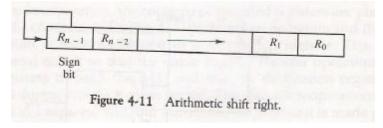

- 3. Arithmetic shift: an arithmetic shift is a micro-operation that shifts a signed binary number to the left or right. An arithmetic shift left multiples a signed binary number by 2 and arithmetic shift right divides the number by 2.

The arithmetic shift must leave the sign bit unchanged because the sign of the number remains the same when it is multiples or divided by 2. The left most bit in register holds the sign bit and the remaining bits hold the numbers. Figure shows a typical register of n bits. Bit  $R_{n-1}$  in the left most position holds the sign bit.  $R_{n-2}$  is the most significant bit of the number and  $R_0$  is the least significant bit. The arithmetic shift-right leaves the sign bit unchanged and shift the number(including the sign bit) to the right. Thus  $R_{n-1}$  remains the same  $R_{n-2}$  receives the bit from  $R_{n-1}$  and so on for other bits in the register. The bit  $R_0$  is lost.

imp

## **Introduction to HDL and VHDL**

Hardware Description Language(HDL) is a specialized computer language used to program the structure, design and operation of electronic circuits and most commonly digital logic circuits.

A hardware description language enables a precise, formal description of an electronic circuits that allows for the automated analysis, simulation and simulated testing of an electronic circuit. It also allows for the compilation of an HDL program into a lower level specification of physical electronic components.

What are the advantages of using HDLs?

- Can express large, complex design.

- Flexible modelling capabilities.

- Description can include the very abstract to the very structural level

- Productivity

- Logic synthesis: easily develop, use the available logics.

- Design changes are fast and easily done.

- Optimization of design is easier.

- Exploration of alternative design can be done quickly.

- Reusability:

- Packages, libraries, design all can be reused.

- Vendors and technology independence

- E.g. CMOS, ECL, gates same code.

- Documentation

- Textual documentation is part of the code, not a separate document.

Example:

// This module creates an address/accumulator

Module adder (

Input clk, // input clock

Input reset\_n, // async active low

Input first\_select, // on first data item use this

Input rd\_fifo, //enable for ff

Input [7:0] data, //data in

Output reg[11:0] acc\_out //data out of accumulator

);

Always @ (posedge clk, nedge reset\_n)

If(!reset\_n) acc\_out<=12'h000;</pre>

Else

If(rd\_fifo==1 'b')

If(first\_selected==1'b') acc\_out<=data</pre>

Else acc\_out<=acc\_out+data;

End module

What can't an HDL do?

- We cannot make architectural tradeoffs, but it can help.

- Does not relieve in understanding digital design.

- If you can't draw the structure you are looking for stop coding.

VDHL(Very High Speed Integrated Circuit (VHSIC) HDL

- More difficult to learn

- Widely used for FPGAs

# Verilog

- Simpler to learn.

- Look like C.

# VHDLs history

- VHDL is the product of US government request for a new means of describing digital hardware.

- VHSIC program was an initiative of the defense department to push the state of the art in VLSI technology and HDL was proposed as a versatile hardware description language.

# Reason for Using VHDL

- International IEEE standard specification language.

- Enables hardware modelling from the gate to system level.

- Provides a mechanism for digital design and design documentation.

- Formal model to communicate.

- Modelling: documentation.

- Testing and validation using simulation.

- Performance prediction.

- Automatic synthesis.

- Concurrency, more than one thing going at a time.

- VHDL allows the designers to work at various levels of abstraction.

- Behavioural, RTL, Boolean equation, gates.

- Allows for various design methodologies, top  $\rightarrow$  down, bottom  $\rightarrow$ up.

- Flexible in describing hardware.

- Provides technology independence.

- Describes a wide variety of digital hardware.

# **Chapter 3 Central Processing Unit**

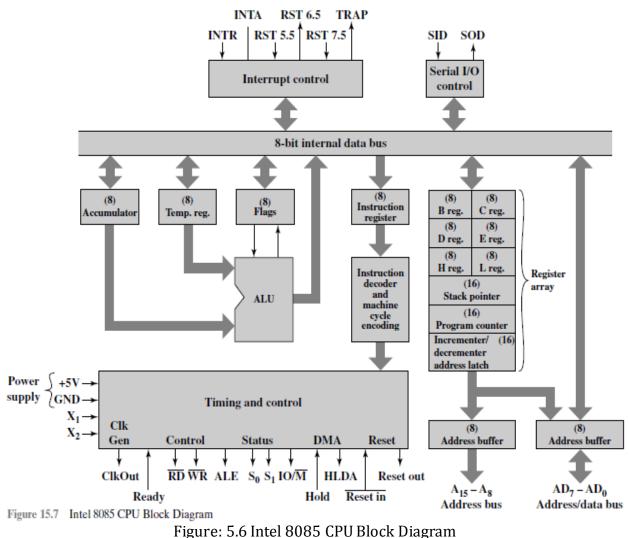

# 3.1 CPU Organization and Structure

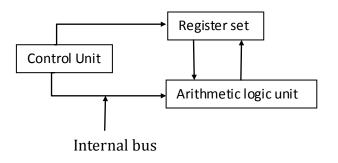

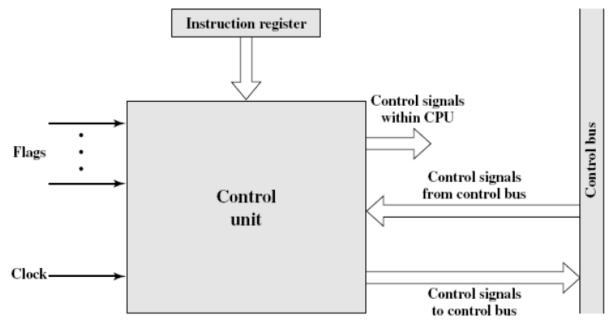

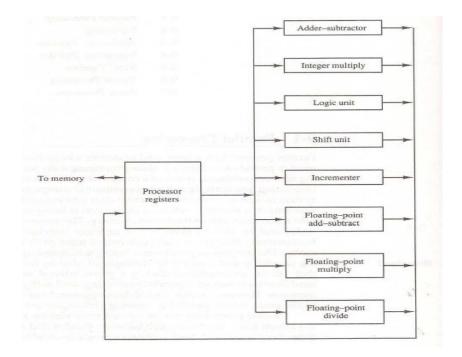

The part of the computer that performs the bulk of data processing operations is called the central processing unit (CPU). The CPU is made of three major parts as in figure:

Figure 3.1: Major Components of CPU

The register set stores immediate data used during the execution of the instructions.

**Control unit:** It supervises the transfer of information among the registers and instructs the ALU (Arithmetic and Logic Unit) as to which operations to perform.

ALU (Arithmetic and logic Unit): Performs all the arithmetic and logical operations.

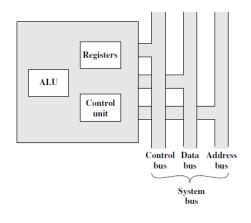

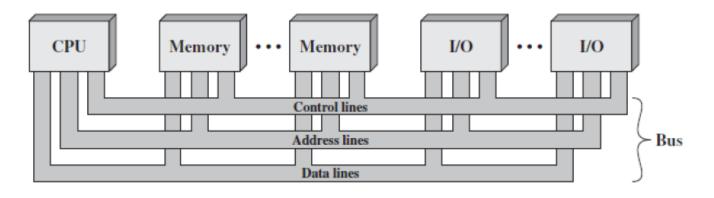

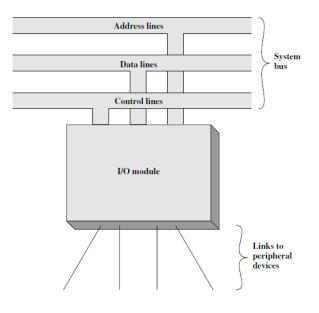

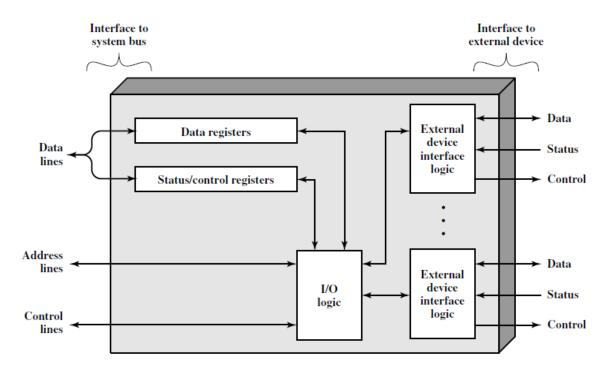

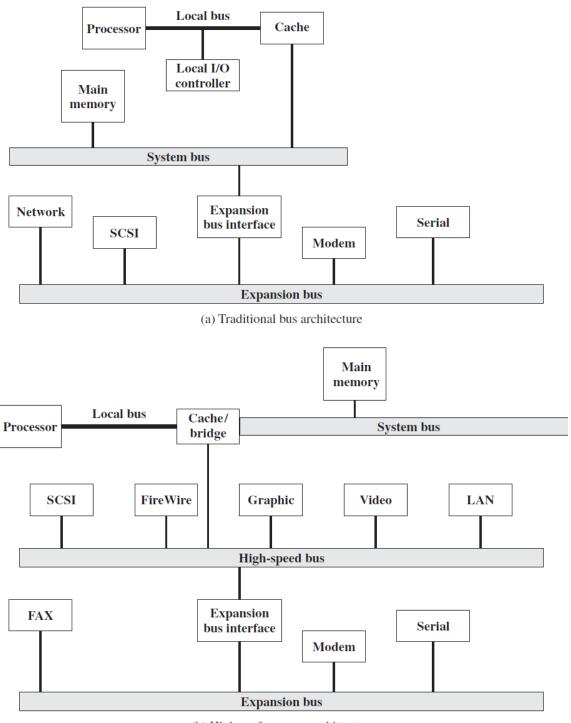

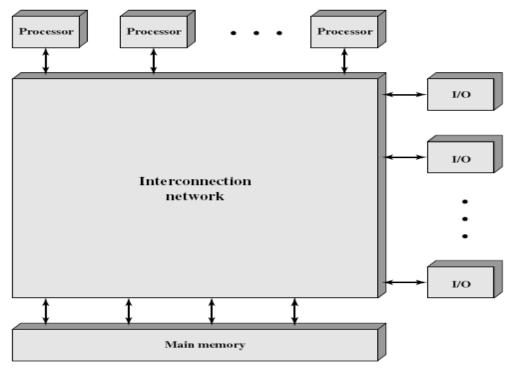

A computer consists of set of components or modules of three basic types (processor, memory, I/O) that communicate with each other. The collection of paths connecting the various modules is called the interconnection structure. The design of this structure will depend on the exchange of data and information that must be made among the modules.

# **Bus interconnection**

A bus is a communication pathway connecting two or more devices, which is shared transmission medium. Multiple devices connect to the bus and a signal transmitted by one device is available for reception by all other devices attached to the bus. If two devices transmit during the same time period their signals will overlap and become garbled, thus only one device can transmit successfully at a time. Typically a bus consists of multiple communication pathways or lines, each lines is capable of transmitting signals representing binary 1 or 0.

Figure 3.2: Bus interconnection Scheme

- Data line: provide a path for moving data among system modules.

- Address line: used to designate the source or destination of the data on data bus.

- Control lines: used to control the access to and use of data and address lines.

Figure 3.3: Internal structure of the CPU

## 3.2 Register organization

Register are faster, smaller and more expensive memory that function as a level of memory above main memory and cache. The two categories to register are:

- a) **User-visible registers:** a user visible register is one that may be referenced by means of the machine language that the processor executes.

- b) **Control and status registers:** Used by the control unit to control the operation of the processor and by privileged, operating system programs to control the execution of programs.

- a) **User-visible registers:** a user visible register is one that may be referenced by means of the machine language that the processor executes. We can further categorize as follows:

- 1. General purpose

- 2. Data

- 3. Address

- 4. Condition codes

- 1. *General-purpose registers* can be assigned to a variety of functions by the programmer. Sometimes their use within the instruction set is orthogonal to the operation. i.e, any generalpurpose register can contain the operand for any op-code. This provides true general-purpose register use. Often, however, there are restrictions. For example, there may be dedicated registers for floating-point and stack operations. In some cases, general-purpose registers can be used for addressing functions (e.g., register indirect, displacement). In other cases, there is a partial or clean separation between data registers and address registers.

- 2. *Data register:* Data registers may be used only to hold data and cannot be employed in the calculation of an operand address.

- 3. *Address registers* may themselves be somewhat general purpose, or they may be devoted to a particular addressing mode. Examples include the following:

- i. *Segment pointers:* In a machine with segmented addressing, a segment register holds the address of the base of the segment. There may be multiple registers: for example, one for the operating system and one for the current process.

- ii. *Index registers:* These are used for indexed addressing and may be auto indexed.

- iii. *Stack pointer:* If there is user-visible stack addressing, then typically there is a dedicated register that points to the top of the stack. This allows implicit addressing; i.e, push, pop, and other stack instructions need not contain an explicit stack operand.

- iv. *Conditional codes (also referred to as flags):* Condition codes are bits set by the processor hardware as the result of operations. For example, an arithmetic operation may produce a positive, negative, zero, or overflow result. In addition to the result itself being stored in a register or memory, a condition code is also set. The code may subsequently be tested as part of a conditional branch operation. Condition code bits are collected into one or more registers. Usually, they form part of a control register. Generally, machine instructions allow these bits to be read by implicit reference, but the programmer cannot alter them.

# b) Control and status register :

There are a variety of processor registers that are employed to control the operation of the processor. Most of these, on most machines, are not visible to the user. Some of them may be visible to machine instructions executed in a control or operating system mode. Of course, different machines will have different register organizations and use different terminology. Four register are essential to instruction execution:

- **1. Program counter (PC):** Contains the address of an instruction to be fetched.

- 2. Instruction register (IR): Contains the instruction most recently fetched.

- 3. Memory Address Register (MAR): Contains the address of a location in memory.

- **4. Memory Buffer Register (MBR):** Contains a word of data to be written to memory or the word most recently read.

Many processor designs include a register or set of registers, often known as the *program status word* (PSW), that contain status information. The PSW typically contains condition codes plus other status information. Common fields or flags include the following:

- Sign: Contains the sign bit of the result of the last arithmetic operation.

- **Zero:** Set when the result is 0.

• **Carry:** Set if an operation resulted in a carry (addition) into or borrow (subtraction) out of a high-order bit. Used for multiword arithmetic operations.

- Equal: Set if a logical compare result is equality.

- **Overflow:** Used to indicate arithmetic overflow.

- Interrupt Enable/Disable: Used to enable or disable interrupts.

• **Supervisor:** Indicates whether the processor is executing in supervisor or user mode. Certain privileged instructions can be executed only in supervisor mode, and certain areas of memory can be accessed only in supervisor mode.

Note: see example of microprocessor register organization MC68000 & intel 8086 from William Stallings book.

# 3.3 Instruction cycle

The processing required for a single instruction is called an *instruction cycle*. The instruction cycle can be simply depicted in Figure 3.3. The two steps are referred to as the *fetch cycle* and the *execute cycle*. Program execution halts only if the machine is turned off, some sort of unrecoverable error occurs, or a program instruction that halts the computer is encountered.

Figure 3.4 Basic instruction cycle

An instruction cycle includes the following stages:

- Fetch: Read the next instruction from memory into the processor.

- **Execute:** Interpret the op-code and perform the indicated operation.

• **Interrupt:** If interrupts are enabled and an interrupt has occurred, save the current process state and service the interrupt. We are now in a position to elaborate somewhat on the instruction cycle. First, we must introduce one additional stage, known as the indirect cycle.

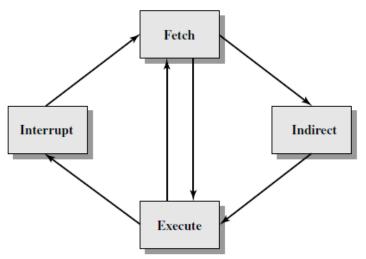

Figure 3.5 instruction cycle

The execution of an instruction may involve one or more operands in memory, each of which requires a memory access. Further, if indirect addressing is used, then additional memory accesses are required. We can think of the fetching of indirect addresses as one more instruction stages. The result is shown in Figure 3.5. The main line of activity consists of alternating instruction fetch and instruction execution activities. After an instruction is fetched, it is examined to determine if any indirect addressing is involved. If so, the required operands are fetched using indirect addressing.

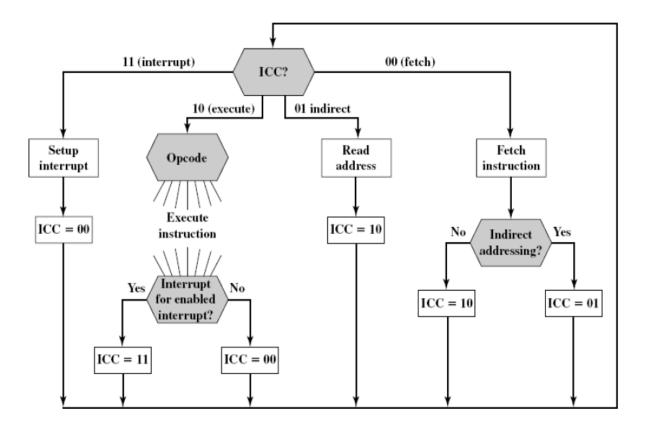

# Instruction cycle state diagram

The figure 3.6 shows the state diagram of instruction cycle. For any given instruction cycle some states may be null and others may be visited more than once. The different states may be described as:

Figure 3.6: Instruction cycle state diagram

**Instruction address calculation (iac):** Determine the address of the next instruction to be executed. Usually, this involves adding a fixed number to the address of the previous instruction. For example, if each instruction is 16 bits long and memory is organized into 16bit words, then add 1 to the previous address. If, instead, memory is organized as individually addressable 8-bit bytes, then add 2 to the previous address. • Instruction fetch (if): Read instruction from its memory location into the processor.

• **Instruction operation decoding (iod)**: Analyze instruction to determine type of operation to be performed and operand(s) to be used.

• **Operand address calculation (oac):** If the operation involves reference to an operand in memory or available via I/O, then determine the address of the operand.

- **Operand fetch (of):** Fetch the operand from memory or read it in from I/O.

- Data operation (do): Perform the operation indicated in the instruction.

• **Operand store (os):** Write the result into memory or out to I/O.

States in the upper part of Figure 3.5 involve an exchange between the processor and either memory or an I/O module. States in the lower part of the diagram involve only internal processor operations. The oac state appears twice, because an instruction may involve a read, a write, or both. Finally, on some machines, a single instruction can specify an operation to be performed on a vector (one-dimensional array) of numbers or a string (one-dimensional array) of characters. As Figure 3.6 indicates, this would involve repetitive operand fetch and/or store operations.

# Interrupts

Interrupts is an asynchronous service request from hardware or software to CPU, interrupts makes CPU execution of its normal operation to pause and then to service external device. The processor and OS are responsible for recognizing an interrupt, suspending the user program servicing the interrupt and then resuming the user program. The instruction cycle with interrupts is as shown in figure.

Figure 3.7 Instruction cycle with interrupt.

Figure 3.8 Instruction cycle state diagram with interrupt

In the interrupt cycle, the processor checks to see if any interrupts have occurred, indicated by the presence of an interrupt signal. If no interrupts are pending, the processor proceeds to the fetch cycle and fetches the next instruction of the current program. If an interrupt is pending, the processor does the following:

- It suspends execution of the current program being executed and saves its context. This means saving the address of the next instruction to be executed (current contents of the program counter) and any other data relevant to the processor's current activity.

- It sets the program counter to the starting address of an *interrupt handler* routine.

The processor now proceeds to the fetch cycle and fetches the first instruction in the interrupt handler program, which will service the interrupt. The interrupt handler program is generally part of the operating system. Typically, this program determines the nature of the interrupt and performs whatever actions are needed.

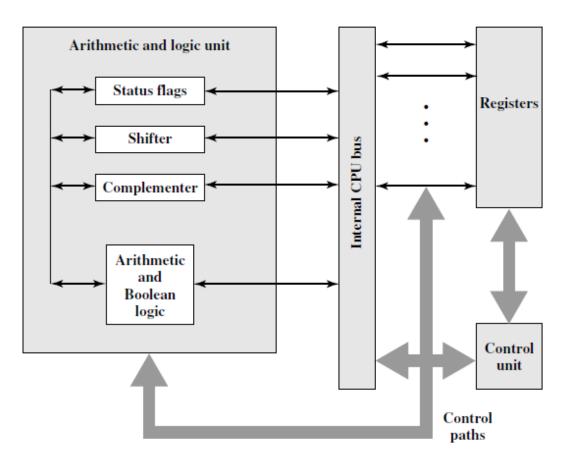

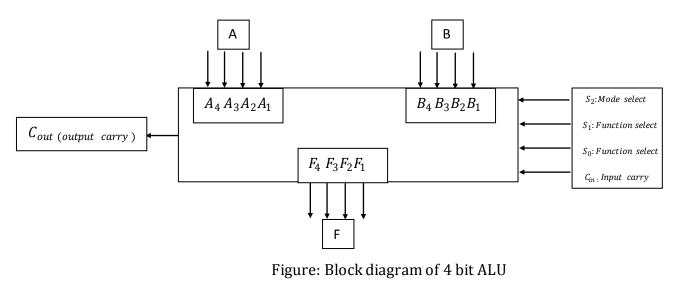

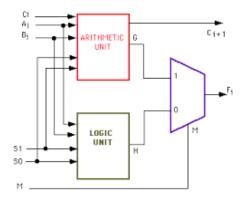

# 3.4 The arithmetic and logic unit

The ALU is that part of the computer that actually performs arithmetic and logical operations on data. ALU is a multi operation combinational logic digital function i.e. can perform set of arithmetic and logic of operations. Figure shows the block diagram of 4 bit ALU.

| S1 | SO | Arithmetic (s2=0) | Logical(s2=1) |

|----|----|-------------------|---------------|

| 0  | 0  | Addition          | OR            |

| 0  | 1  | Subtraction       | AND           |

| 1  | 0  | Multiplication    | NOT           |

| 1  | 1  | Division          | Ex-OR         |

The selection lines are decodes within the ALU so that the K selection variables can specify up to  $2^k$  distinct operations. Figure shows 4 bit inputs A and B to generate 4 bit result F. The mode select distinguish between arithmetic and logic operations. The two function select inputs specify the particular arithmetic or logical operations.

# 3.5 Design principles of Modern System

- Efficient memory utilization.

- Use of caches, different levels.

- Improvement in input and output mechanism.

- Pipelining.

- Parallel processing.

- Multi-core systems.

# **Chapter 4 Computer Arithmetic**

# 4.1 Integer Representation

In the binary number system, arbitrary numbers can be represented with just two digits zero and one, the minus sign, and the period, or **radix point**. E.g -1101.01012 = -13.312510. For purposes of computer storage and processing, however, we do not have the benefit of minus signs and periods. Only binary digits (0 and 1) may be used to represent numbers. If we are limited to nonnegative integers, the representation is straightforward.

An eight bit word can be represented as 0=0000000, 1=0000001, 7=00000111.

In general, if an n-bit sequence of binary digits is interpreted as an unsigned integer A, its value is

$A=\sum_{i=0}^{n-1} 2^i a_i$

# 4.1.1 Sign-Magnitude Representation

There are several alternative conventions used to represent negative as well as positive integers, all of which involve treating the most significant (leftmost) bit in the word as a sign bit. If the sign bit is 0, the number is positive; if the sign bit is 1, the number is negative. The simplest form of representation that employs a sign bit is the sign-magnitude representation. In an n-bit word, the rightmost bits hold the magnitude of the integer.

+ 7 = 0111; -7 = 1111 (sign magnitude)

# Drawbacks

- Addition and subtraction requires a consideration of both sign of numbers and their relative magnitudes to carry out the required operation.

- Two representations for 0.

# 4.1.1.1 Two's complement representation

Like sign magnitude two's complement representation uses the most significant bit as sign bit making it easy to test whether the integer is negative or positive. It differs from the use of sign magnitude representation in the way the other bits are interpreted.

Method:

For negation take the Boolean complement of each bits of corresponding positive number, and then add one to the resulting bit pattern.

Consider n nit integer A in two's complement representation. If A is positive then the sign bit  $a_{n-1 \text{ zero}}$ . The remaining bit represents the magnitude of the number.

A= $\sum_{i=0}^{n-1} 2^i a_i$ . The range of positive integer that may be represented is 0- 2<sup>n-1</sup>-1.

Now for negative numbers integer A, the sign bit  $a_{n-1}$  is 1. The range of negative integer that can be represented is from -1 to  $-2^{n-1}$

|    | Sign representation | Two's complement |

|----|---------------------|------------------|

| +7 | 0111                | 0111             |

| -7 | 1111                | 1001             |

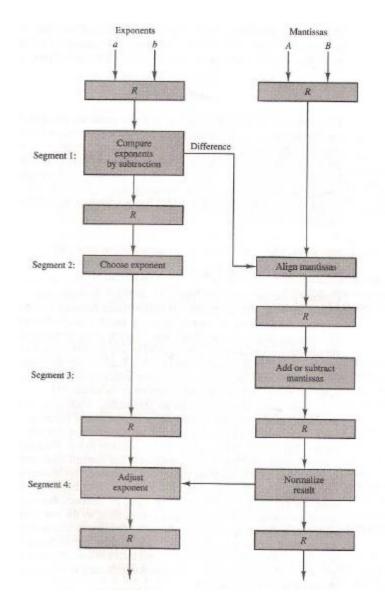

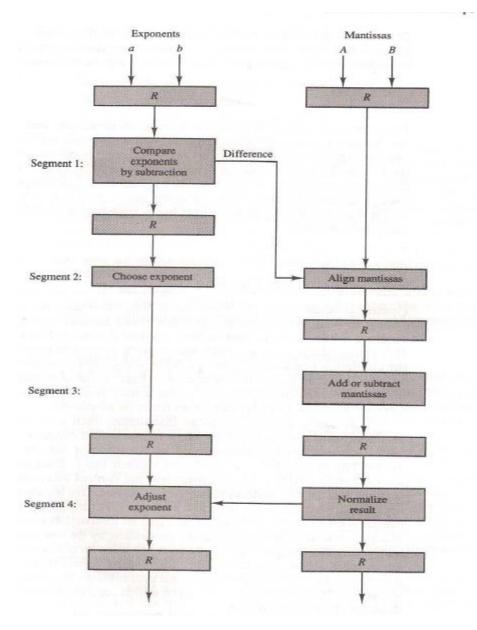

#### 4.1.1.2 Float point representation

MRE

The float point representation of a number has two parts. The first part represents a signed, fixed point number called mantissa. The second part gives the position of the decimal point called exponent.

|           | Fraction   | Exponent |

|-----------|------------|----------|

| +6132.789 | +0.6132789 | +04      |

#### 0.6132789 x 10 <sup>4</sup>

In the same it can be used for binary numbers.

|          | Fraction  | Exponent |

|----------|-----------|----------|

| +1001.11 | 0.1001110 | 000100   |

(0.1001110) x 2<sup>4</sup>

Only the mantissa m and the exponent e are physically represented in the register (including their signs).

#### Negation

In sign magnitude negation is done by inverting the sign bit.

In two's complement method:

• Take Boolean complement if each bit. Then add 1

#### 4.2 Integer Arithmetic

#### 4.2.1 Addition and subtraction with sign twos complement data

#### Addition

| 0011   |  |

|--------|--|

| + 0100 |  |

| 0111   |  |

#### Subtraction

M-N

- 1. Add M to r's complement of N.

- 2. Inspect the result obtained in step 1 for an end carry.

- a. If an end carry occurs discard it.

- b. If an end carry does not occur take r's complement of the number obtained in step 1 and place a negative sign in front.

#### M-N, M=1010100, N=1000100

```

1's complement of N= 0111011

```

```

2's complement of N= (0111011+1) =0111100

```

1010100

+ 0111100

10010000

Here end carry is generated , so discard it, hence final answer is 0010000

#### M=1000100, N=1010100

1's complement of N= 0101011

#### 2's complement of N= (0101011+1) =0101100

| 1000100                                                                    |

|----------------------------------------------------------------------------|

| + 0101100                                                                  |

| 111000                                                                     |

| Here no end carry, take 2's complement of 111000 and place a negative sign |

| =-10000                                                                    |

On any addition the result may be larger than the word size being used then it is called overflow. When overflow occurs the ALU must signal so that the process is stopped.

#### Overflow rule

If two numbers are added and they are both positive or negative, then overflow occurs if and only if the result has opposite sign.

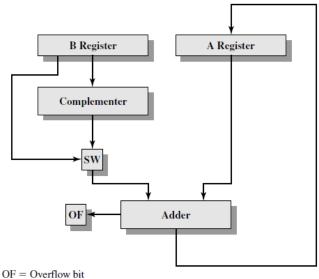

SW = Switch (select addition or subtraction)

Figure 4.1: block diagram of hardware for addition and subtraction

- Figure shows the data path and hardware elements needed to accomplish addition and subtraction.

- Binary adder is the central element for addition to produce sum and overflow indication.

- For addition of two number in register A and B passed to adder.

- For subtraction the subtrahend (register B) is 2's complemented and added so that the nos. are subtracted.

- Overflow indication stored in 1 bit overflow flag, 0= no overflow, 1= overflow.

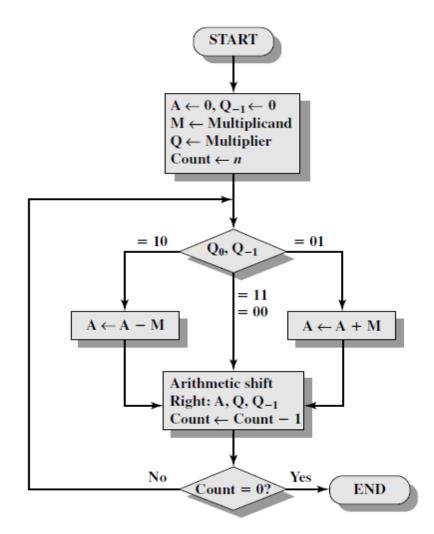

#### 4.4 Unsigned Binary Multiplication Algorithm

#### 4.4.1 Multiplication

Compared with addition and subtraction, multiplication is a complex operation, whether performed in hardware or software.

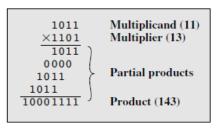

Figure 4.2 : multiplication of unsigned binary integers

This method is not efficient for computer operations so for computer operation, we follow the following algorithms for unsigned number.

Figure 4.3: flow chart for unsigned binary multiplication

Example: 1101x1011=1000111, 13x11=143

| Count | С | А    | Q    | М    | operations     |

|-------|---|------|------|------|----------------|

| 4     | 0 | 0000 | 1101 | 1011 | Initial values |

|       | 0 | 1011 | 1101 | 1011 | Add(A+M)       |

| 3     | 0 | 0101 | 1110 | 1011 | Shift(right)   |

| 2     | 0 | 0010 | 1111 | 1011 | Shift(right)   |

|       | 0 | 1101 | 1111 | 1011 | Add(A+M)       |

| 1     | 0 | 0110 | 1111 | 1011 | Shift(right)   |

|       | 1 | 0001 | 1111 | 1011 | Add            |

| 0     | 0 | 1000 | 1111 | 1011 | Shift(right)   |

Final value AQ= (10001111)<sub>2</sub>

Perform for 7\*-3=-21

Compiled By: Chayan Hada

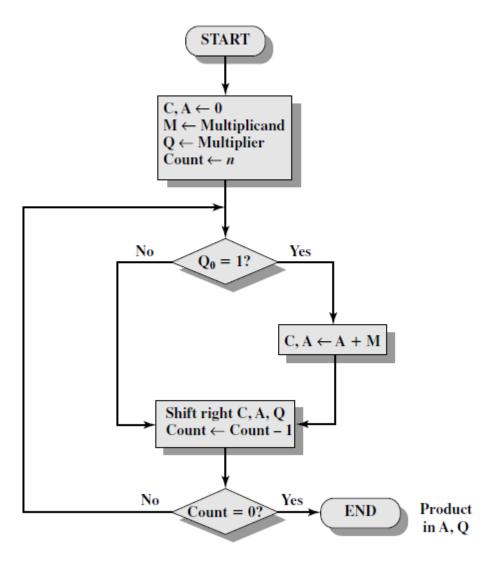

#### 4.5 Booths algorithm

Multiplication of signed number or negative number is not possible by above method so for that we need booths algorithm

Figure 4.4: flowchart of booth's algorithm for two's complement multiplication.

| Perform: 7x-3=-21= (11101011) <sub>2</sub> |

|--------------------------------------------|

|                                            |

| Count | A    | Q    | Q-1 | М    | operations     |

|-------|------|------|-----|------|----------------|

| 4     | 0000 | 0111 | 0   | 1101 | Initial values |

|       | 0011 | 0111 | 0   | 1101 | A←A-M          |

| 3     | 0001 | 1011 | 1   | 1101 | Shift          |

| 2     | 0000 | 1101 | 1   | 1101 | Shift          |

| 1     | 0000 | 0110 | 1   | 1101 | Shift          |

|       | 1101 | 0110 | 1   | 1101 | A←A+M          |

| 0     | 1110 | 1011 | 0   | 1101 | Shift          |

$AQ = (11101011)_2$

Compiled By: Chayan Hada

#### 4.6 Unsigned Binary Division Algorithm

#### Algorithm

- 1. Load M with divisor, AQ with dividend (using sign bit).

- 2. Shift AQ left 1 position (logical shift).

- 3. If M and A have same sign, A  $\leftarrow$  A-M, else A  $\leftarrow$  A+M

- 4.  $Q_0 \leftarrow 1$ , if sign bit of A has not changed.

#### Else $Q_0=0$ and restore A.

- 5. Repeat 2 to 4 till counter is Zero.

- 6. Remainder in A and quotient in Q.

| Example: | 5/2 | = 2, | 1 |

|----------|-----|------|---|

|----------|-----|------|---|

| Count   | А    | Q    | М    | -M   | operation      |

|---------|------|------|------|------|----------------|

| 4       | 0000 | 0101 | 0010 | 1110 | Initial values |

|         | 0000 | 1010 | 0010 | 1110 | Shift AQ       |

| Changed | 1110 | 1010 | 0010 | 1110 | A←A-M          |

| 3       | 0000 | 1010 | 0010 | 1110 |                |

|         | 0001 | 0100 | 0010 | 1110 | Shift AQ       |

| changed | 1111 | 0100 |      |      | A←A-M          |

| 2       | 0001 | 0100 | 0010 | 1110 |                |

|         | 0010 | 1000 | 0010 | 1110 | Shift AQ       |

| Not     | 0000 | 1000 |      |      | A←A-M          |

| 1       | 0000 | 1001 | 0010 | 1110 |                |

|         | 0001 | 0010 |      |      | Shift AQ       |

| Changed | 1111 | 0010 |      |      | A←A-M          |

| 0       | 0001 | 0010 | 0010 | 1110 |                |

Remainder=A=0001, quotient =Q=0010

Do for 7/3

#### 4.7 BCD arithemtic Unit

#### **BCD Adder**

Consider the arithmetic addition of two decimal digits in BCD, together with an input carry from a previous stage. Since each input digit does not exceed 9, the output sum cannot be greater than 9 + 9 + 1 = 19, the 1 in the sum being an input carry. Suppose we apply two BCD digits to a four-bit binary adder. The adder will form the sum in *binary* and produce a result that ranges from 0 through 19.

|   | Binary Sum |                |                |            |   | BCD Sum    |            |                |            |    |

|---|------------|----------------|----------------|------------|---|------------|------------|----------------|------------|----|

| K | <b>Z</b> 8 | Z <sub>4</sub> | Z <sub>2</sub> | <b>Z</b> 1 | c | <b>S</b> 8 | <b>S</b> 4 | S <sub>2</sub> | <b>S</b> 1 |    |

| 0 | 0          | 0              | 0              | 0          | 0 | 0          | 0          | 0              | 0          | 0  |

| 0 | 0          | 0              | 0              | 1          | 0 | 0          | 0          | 0              | 1          | 1  |

| 0 | 0          | 0              | 1              | 0          | 0 | 0          | 0          | 1              | 0          | 2  |

| 0 | 0          | 0              | 1              | 1          | 0 | 0          | 0          | 1              | 1          | 3  |

| 0 | 0          | 1              | 0              | 0          | 0 | 0          | 1          | 0              | 0          | 4  |

| 0 | 0          | 1              | 0              | 1          | 0 | 0          | 1          | 0              | 1          | 5  |

| 0 | 0          | 1              | 1              | 0          | 0 | 0          | 1          | 1              | 0          | 6  |

| 0 | 0          | 1              | 1              | 1          | 0 | 0          | 1          | 1              | 1          | 7  |

| 0 | 1          | 0              | 0              | 0          | 0 | 1          | 0          | 0              | 0          | 8  |

| 0 | 1          | 0              | 0              | 1          | 0 | 1          | 0          | 0              | 1          | 9  |

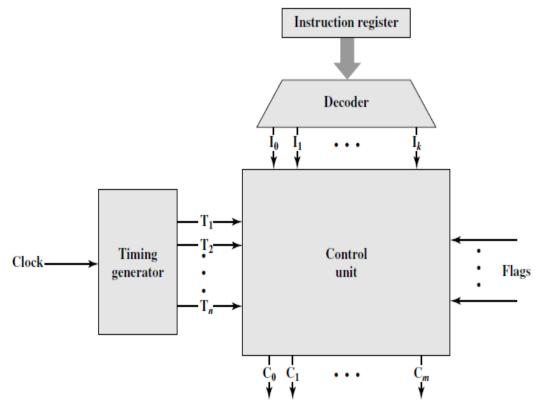

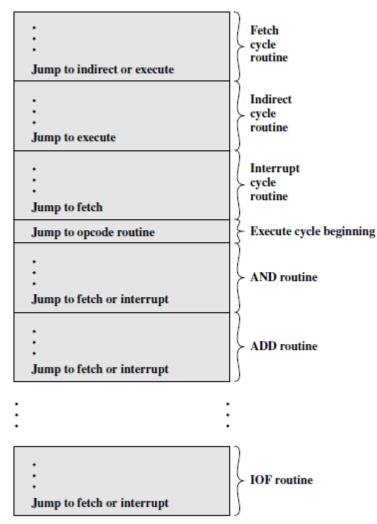

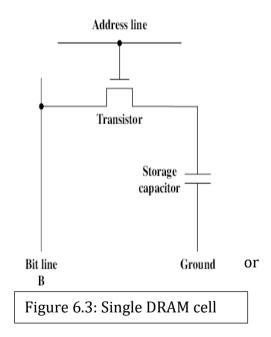

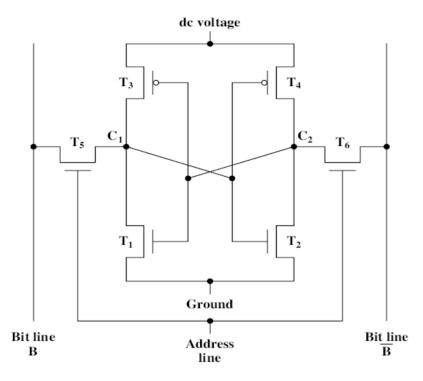

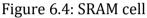

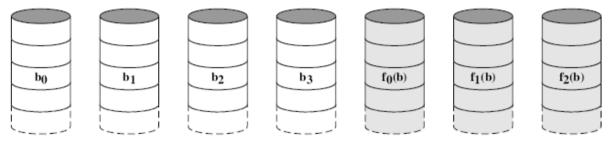

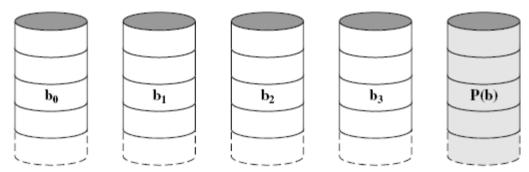

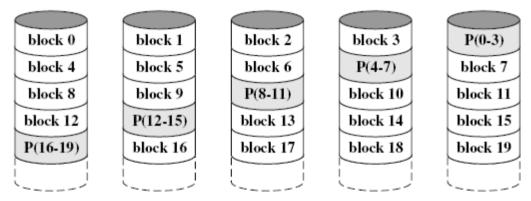

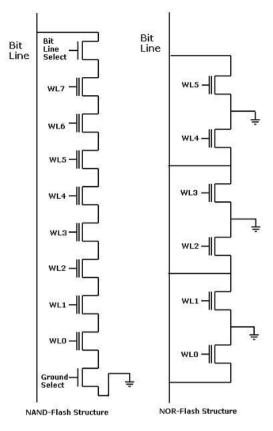

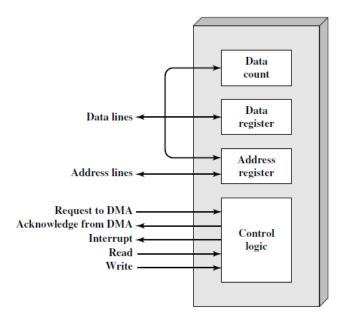

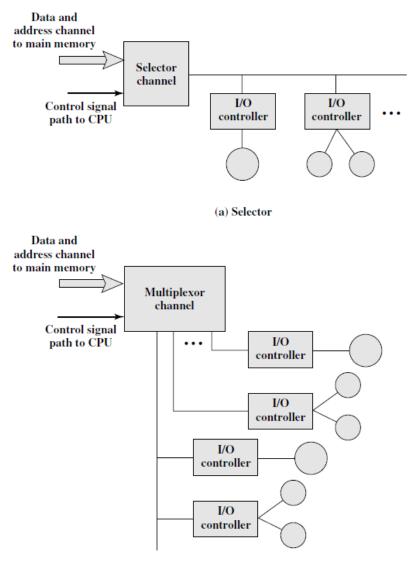

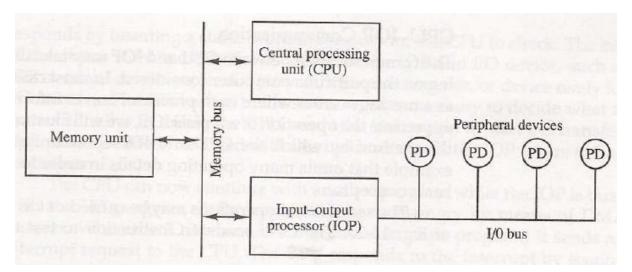

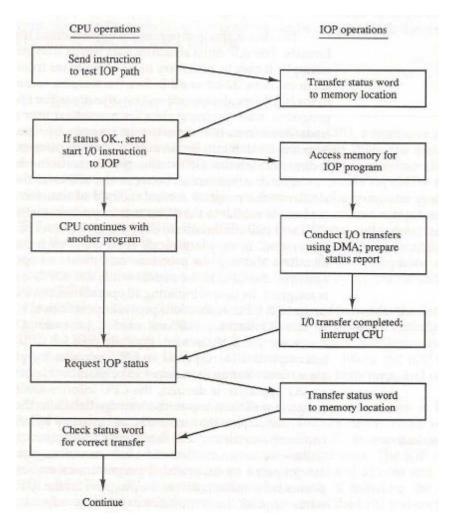

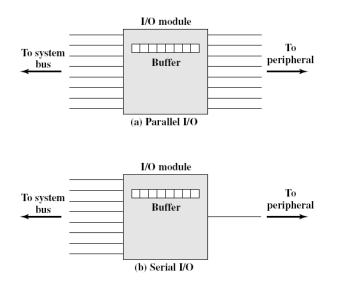

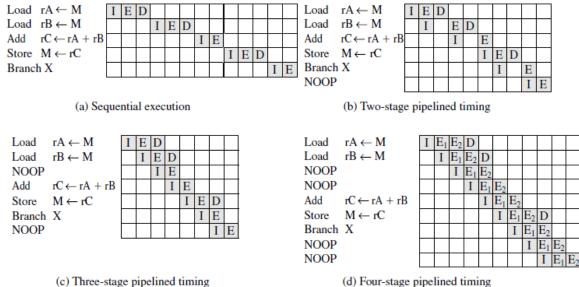

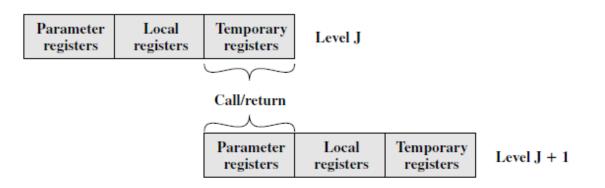

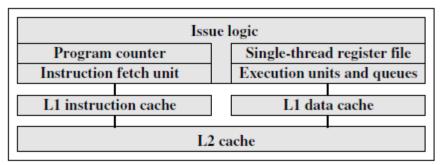

| 0 | 1          | 0              | 1              | 0          | 1 | 0          | 0          | 0              | 0          | 10 |